Tugas 11 Lingga 1903015140 Counter

Counter

Menurut Wikipedia, dalam logika dan komputasi digital, Penghitung adalah

perangkat yang menyimpan (dan terkadang menampilkan) berapa kali peristiwa

atau proses tertentu telah terjadi, sering kali dalam kaitannya dengan sinyal

jam. Penghitung digunakan dalam elektronik digital untuk tujuan penghitungan,

mereka dapat menghitung peristiwa tertentu yang terjadi di sirkuit. Misalnya,

di penghitung UP, penghitung meningkatkan hitungan untuk setiap tepi jam yang

naik. Tidak hanya menghitung, penghitung dapat mengikuti urutan tertentu

berdasarkan desain kami seperti urutan acak 0,1,3,2… Mereka juga dapat

dirancang dengan bantuan flip-flops.

Jenis khusus dari rangkaian sekuensial yang digunakan untuk menghitung pulsa

dikenal sebagai pencacah, atau kumpulan flip flop di mana sinyal clock

diterapkan dikenal sebagai pencacah.

Penghitung adalah salah satu aplikasi terluas dari flip flop. Berdasarkan

pulsa clock, output dari pencacah berisi keadaan yang telah ditentukan.

Jumlah pulsa dapat dihitung dengan menggunakan output dari counter.

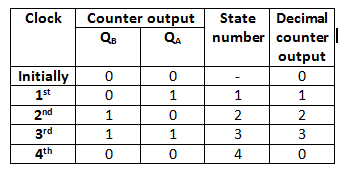

Tabel Kebenaran

Klasifikasi Counter

Counter secara luas dibagi menjadi dua kategori:

Counter asinkron

Counter sinkron

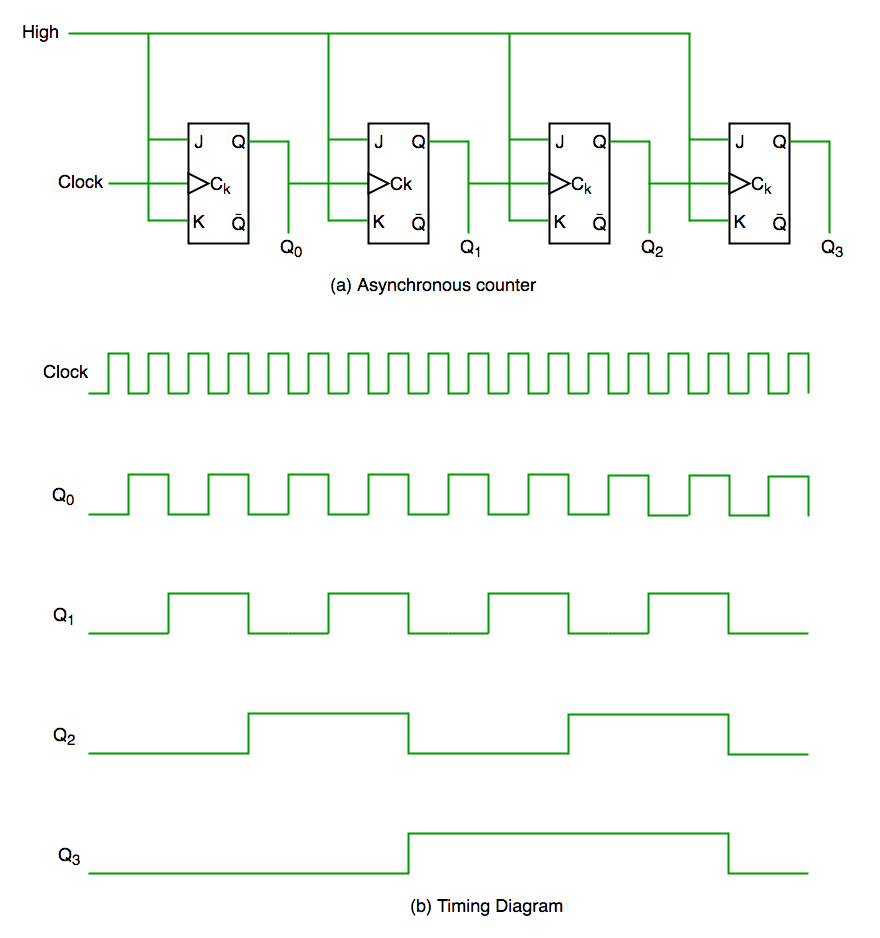

1. Penghitung Asinkron

Dalam pencacah asinkron kami tidak menggunakan jam universal, hanya flip

flop pertama yang digerakkan oleh jam utama dan input jam dari sisa flip

flop berikutnya didorong oleh keluaran flip flop sebelumnya. Kita dapat

memahaminya dengan mengikuti diagram-

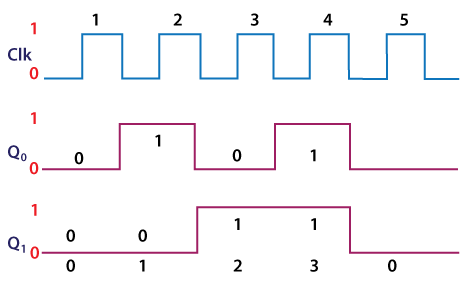

Jelas dari diagram waktu bahwa Q0 berubah segera setelah tepi naik pulsa clock

ditemui, Q1 berubah ketika tepi naik Q0 ditemui (karena Q0 seperti pulsa clock

untuk flip flop kedua) dan seterusnya. Dengan cara ini riak dihasilkan melalui

Q0,Q1,Q2,Q3 sehingga disebut juga pencacah RIPPLE.

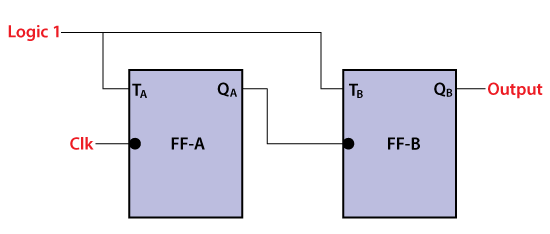

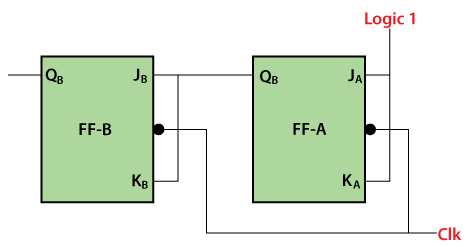

Pencacah asinkron juga dikenal sebagai pencacah riak. Di bawah ini adalah

diagram pencacah Asinkron 2-bit di mana kami menggunakan dua flip-flop T.

Selain flip flop T, kita juga dapat menggunakan flip flop JK dengan menyetel

kedua input ke 1 secara permanen. Jam eksternal diteruskan ke input jam dari

flip flop pertama, yaitu, FF-A dan outputnya, yaitu, diteruskan ke input jam

dari flip flop berikutnya, yaitu, FF-B.

Signal Diagram

Operasi

Kondisi 1: Saat kedua flip flop dalam kondisi reset.

Operasi: Output dari kedua flip flop, yaitu QA QB, akan menjadi 0.

Kondisi 2: Ketika tepi jam negatif pertama lewat.

Operasi: Flip flop pertama akan toggle, dan output dari flip flop ini akan

berubah dari 0 menjadi 1. Output dari flip flop ini akan diambil oleh input

clock dari flip flop berikutnya. Output ini akan diambil sebagai jam tepi

positif oleh flip flop kedua. Masukan ini tidak akan mengubah keadaan keluaran

flip flop kedua karena ini adalah flip flop yang dipicu oleh tepi negatif.

Jadi, QA = 1 dan QB = 0

Kondisi 3: Ketika tepi jam negatif kedua diterapkan.

Operasi: Flip flop pertama akan beralih lagi, dan output dari flip flop ini

akan berubah dari 1 menjadi 0. Output ini akan diambil sebagai jam tepi

negatif oleh flip flop kedua. Masukan ini akan mengubah keadaan keluaran flip

flop kedua karena merupakan tepi negatif yang dipicu flip flop.

Jadi, QA = 0 dan QB = 1.

Kondisi 4: Ketika tepi jam negatif ketiga diterapkan.

Operasi: Flip flop pertama akan beralih lagi, dan output dari flip flop ini

akan berubah dari 0 menjadi 1. Output ini akan diambil sebagai jam tepi

positif oleh flip flop kedua. Masukan ini tidak akan mengubah keadaan keluaran

flip flop kedua karena ini adalah flip flop yang dipicu oleh tepi negatif.

Jadi, QA = 1 dan QB = 1

Kondisi 5: Ketika tepi jam negatif keempat diterapkan.

Operasi: Flip flop pertama akan beralih lagi, dan output dari flip flop ini

akan berubah dari 1 menjadi 0. Output ini akan diambil sebagai jam tepi

negatif oleh flip flop kedua. Masukan ini akan mengubah keadaan keluaran dari

flip flop kedua.

Jadi, QA = 0 dan QB = 0

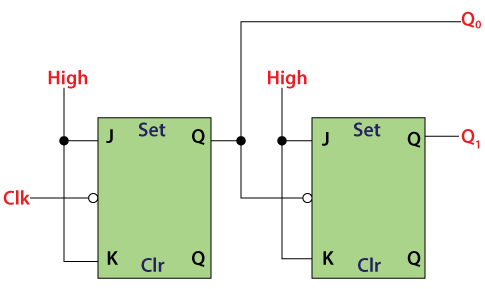

2. Penghitung Sinkron

Berbeda dengan pencacah asinkron, pencacah sinkron memiliki satu jam global yang menggerakkan setiap flip flop sehingga keluaran berubah secara paralel. Salah satu keuntungan pencacah sinkron dibandingkan pencacah asinkron adalah, ia dapat beroperasi pada frekuensi yang lebih tinggi daripada pencacah asinkron karena tidak memiliki penundaan kumulatif karena jam yang sama diberikan untuk setiap flip flop.

Pada pencacah asinkron, keluaran pencacah saat ini diteruskan ke masukan pencacah berikutnya. Jadi, penghitung terhubung seperti rantai. Kekurangan dari sistem ini adalah menimbulkan delay pencacahan, dan penundaan propagasi juga terjadi selama tahap pencacahan. Penghitung sinkron dirancang untuk menghilangkan kelemahan ini.

Pada pencacah sinkron, pulsa clock yang sama dilewatkan ke input clock dari semua flip-flop. Sinyal clock yang dihasilkan oleh semua flip flop adalah sama satu sama lain. Di bawah ini adalah diagram pencacah sinkron 2-bit di mana input flip-flop pertama, yaitu FF-A, diatur ke 1. Jadi, flip-flop pertama akan bekerja sebagai flip-flop toggle. Output dari flip flop pertama dilewatkan ke kedua input dari flip flop JK berikutnya.

Synchronous counter circuit

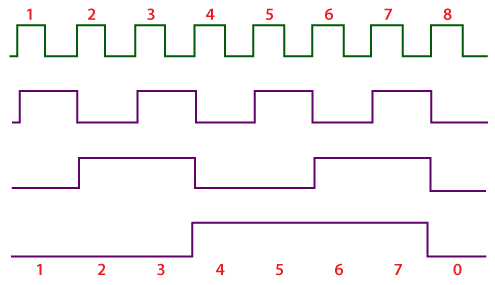

Penghitung sinkron diagram waktu

Dari diagram rangkaian kita melihat bahwa bit Q0 memberikan respon untuk setiap tepi jatuh jam sementara Q1 tergantung pada Q0, Q2 tergantung pada Q1 dan Q0, Q3 tergantung pada Q2, Q1 dan Q0.

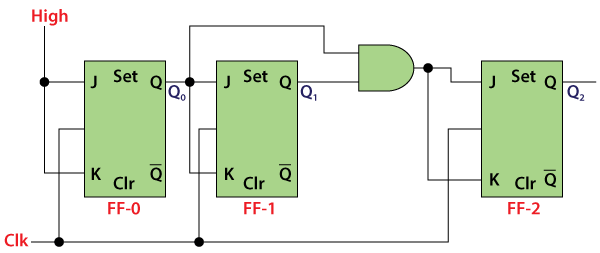

Logical Diagram

Signal Diagram

Operation

Kondisi 1: Saat kedua flip flop dalam kondisi reset.

Operasi: Output dari kedua flip flop, yaitu QA QB, akan menjadi 0.

Jadi, QA = 0 dan QB = 0

Kondisi 2: Ketika tepi jam negatif pertama lewat.

Operasi: Flip-flop pertama akan di-toggle, dan output dari flip-flop ini akan diubah dari 0 menjadi 1. Ketika tepi clock negatif pertama dilewatkan, output dari flip-flop pertama akan menjadi 0. Input clock dari flip flop pertama dan kedua inputnya akan diatur ke 0. Dengan cara ini, keadaan flip flop kedua akan tetap sama.

Jadi, QA = 1 dan QB = 0

Kondisi 3: Ketika tepi jam negatif kedua dilewatkan.

Operasi: Flip-flop pertama akan di-toggle kembali, dan output dari flip-flop ini akan berubah dari 1 menjadi 0. Ketika tepi clock negatif kedua dilewatkan, output dari flip-flop pertama akan menjadi 1. Input clock dari flip flop pertama dan kedua inputnya akan disetel ke 1. Dengan cara ini, keadaan flip flop kedua akan berubah dari 0 menjadi 1.

Jadi, QA = 0 dan QB = 1

Kondisi 4: Ketika tepi jam negatif ketiga lewat.

Operasi: Flip flop pertama akan beralih dari 0 ke 1, tetapi pada saat ini, baik input dan input clock disetel ke 0. Oleh karena itu, output akan tetap sama seperti sebelumnya.

Jadi, QA = 1 dan QB = 1

Kondisi 5: Ketika tepi jam negatif keempat lewat.

Operasi: Flip flop pertama akan beralih dari 1 ke 0. Pada saat ini, input dan input clock dari flip flop kedua diatur ke 1. Oleh karena itu, output akan berubah dari 1 ke 0.

Jadi, QA = 0 dan QB = 0

Decade Counter

Penghitung dekade menghitung sepuluh status berbeda dan kemudian mengatur ulang ke status awalnya. Penghitung dekade sederhana akan menghitung dari 0 hingga 9 tetapi kami juga dapat membuat penghitung dekade yang dapat melewati sepuluh status antara 0 hingga 15 (untuk penghitung 4 bit).

Clock pulse Q3 Q2 Q1 Q0

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1

10 0 0 0 0

Truth table for simple decade counter

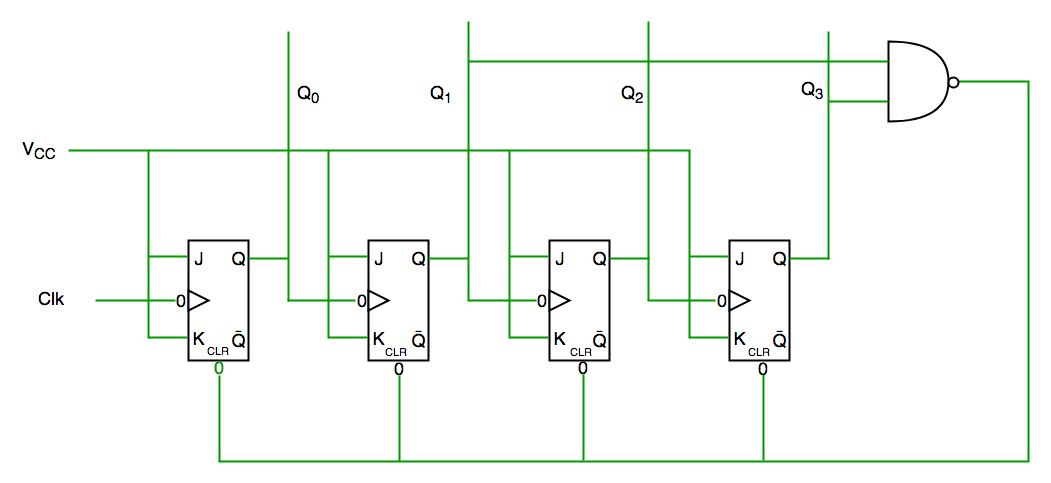

Decade counter circuit diagram

Kami melihat dari diagram rangkaian bahwa kami telah menggunakan gerbang nand untuk Q3 dan Q1 dan mengumpankannya untuk menghapus jalur input karena representasi biner dari 10 adalah—

1010

Dan kita melihat Q3 dan Q1 adalah 1 di sini, jika kita memberikan NAND dari dua bit ini untuk menghapus input maka penghitung akan menjadi kosong pada 10 dan mulai lagi dari awal.

Poin penting: Jumlah flip flop yang digunakan pada pencacah selalu lebih besar dari sama dengan (log2 n) di mana n=jumlah keadaan pada pencacah.

Contoh Soal & Jawaban:

1. Sebuah S-R latch input HIGH aktif dibentuk oleh cross-coupling dari

a) dua gerbang NOR

b) dua gerbang NAND

c) dua gerbang OR

d) dua gerbang AND

Jawaban: A.

2. Untuk kombinasi input D dan EN apa yang akan direset D latch?

a) D = LOW, EN = LOW

b) D = LOW, EN = HIGH

c) D = HIGH, EN = LOW

d) D = HIGH, EN = HIGH

Jawaban: B.

3. Sebuah flip-flop mengubah keadaannya selama

a) siklus operasional lengkap

b) tepi jatuh dari dorongan waktu

c) tepi naik dari dorongan waktu

d) 3 inputs and 3 outputs

Jawaban: D.

4. Tujuan dari input clock ke flip-flop adalah untuk

a) bersihkan perangkat

b) mengatur perangkat

c) selalu menyebabkan output berubah status

d) menyebabkan output mengasumsikan keadaan bergantung pada input pengontrol (J-K atau D).

Jawaban: D.

5. Untuk D flip-flop dipicu oleh tepi,

a) perubahan keadaan flip-flop hanya dapat terjadi pada tepi dorongan clock

b) keadaan flip-flop bergantung pada input D

c) output mengikuti input pada setiap dorongan clock

d) semua jawaban benar

Jawaban: D.

6. Ciri yang membedakan J-K flip-flop dari D flip-flop adalah.

a) toggle condition

b) preset input

c) type of clock

d) clear input

Jawaban: A.

7. Sebuah flip-flop SET ketika

a) J = 0, K = 0

b) J = 0, K = 1

c) J = 1, K = 0

d) J = 1, K = 1

Jawaban: C.

8. J-K flip-flop dengan J = 1 dan K = 1 memiliki input clock 10 kHz. Output Q adalah

a) terus-menerus HIGH

b) terus-menerus LOW

c) gelombang persegi 10 kHz

d) gelombang persegi 5 kHz

Jawaban: D.

9. J-K flip-flop dapat dibuat dari S-R flip-flop dengan menggunakan dua tambahan

a) AND gate

b) OR gate

c) NOT gate

d) NOR gate

Jawaban: A.

10. Latch yang dibangun dengan gerbang NOR dan NAND cenderung tetap dalam kondisi terkunci karena fitur konfigurasi yang mana?

a) Asynchronous operation

b) low input voltage

c) gate impedance

d) cross coupling

Jawaban: B.

Sumber:

> https://onlinelearning.uhamka.ac.id

> https://www.javatpoint.com/counters-in-digital-electronics

> https://www.geeksforgeeks.org/counters-in-digital-logic/

> https://engineeringinterviewquestions.com/mcqs-on-counters-answers/

Comments

Post a Comment