Tugas 9 Lingga 1903015140 Latches, Flip-Flops, and Timer

Latches, Flip-Flops, and Timer

Latches

Latch adalah tipe khusus dari rangkaian logika. Latches memiliki dua status stabil low dan high. Karena keadaan ini, latches juga disebut sebagai multivibrator bistabil(bistable-multivibrators). Latch adalah perangkat penyimpanan yang menyimpan data menggunakan jalur umpan balik. Latch menyimpan 1 -bit hingga perangkat disetel ke 1. Latch mengubah data yang disimpan dan terus-menerus menguji input saat input yang diaktifkan disetel ke 1.

Berdasarkan sinyal aktifkan, rangkaian bekerja dalam dua keadaan. Ketika input aktifkan tinggi, maka kedua input rendah, dan ketika input aktifkan rendah, kedua input tinggi.

Jenis-Jenis Latches

SR Latch

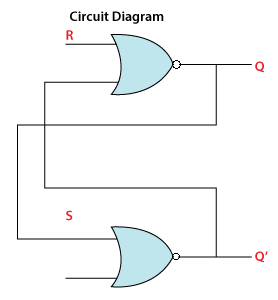

SR Latch adalah jenis khusus perangkat asinkron yang bekerja secara terpisah untuk sinyal kontrol. Itu tergantung pada S-states dan R-inputs. Desain SR latch dengan menghubungkan dua gerbang NOR dengan koneksi cross loop. SR Latch juga dapat dirancang menggunakan gerbang NAND. Di bawah ini adalah diagram rangkaian dan tabel kebenaran SR Latch.

Truth Table

| S | R | Q | Q' |

|---|---|---|---|

| 0 | 0 | latch | Latch |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

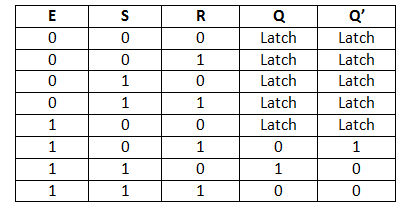

Gated SR Latch

Gated SR Latch adalah jenis khusus SR Latch yang memiliki tiga input, yaitu Set, Reset, dan Enable. Enable input harus aktif agar input SET dan RESET menjadi efektif. Input ENABLE dari SR Latch yang terjaga keamanannya memungkinkan pengoperasian input SET dan RESET. Input ENABLE ini terhubung dengan sakelar. Input Set-Reset diaktifkan saat sakelar ini aktif. Jika tidak, semua perubahan akan diabaikan dalam input set dan reset. Di bawah ini adalah diagram sirkuit dan tabel kebenaran SR Latch Bergerbang.

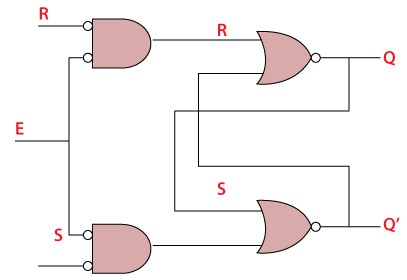

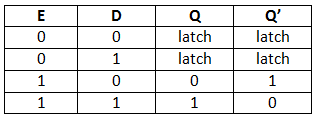

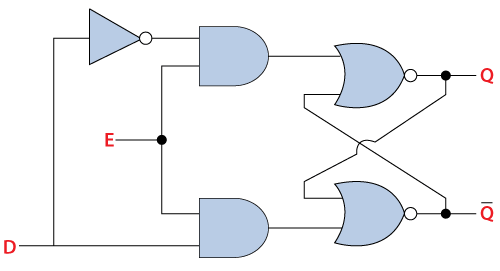

D Latch

D latch sama dengan D flip flop. Satu-satunya perbedaan antara keduanya adalah ENABLE input. Keluaran latch sama dengan masukan yang diteruskan ke input Data saat ENABLE input disetel ke 1. Pada saat itu, latch terbuka, dan jalurnya transparan dari input ke output. Jika ENABLE input diatur ke 0, output D latch adalah nilai terakhir latch, yaitu, independen dari input D, dan latch ditutup. Di bawah ini adalah diagram rangkaian dan tabel kebenaran D latch.

Gated D Latch

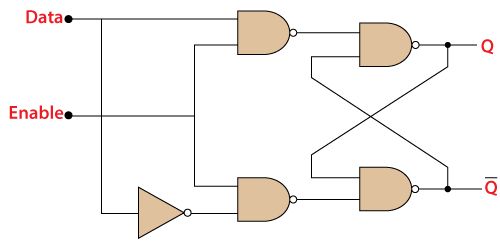

Gated D Latch adalah jenis khusus lain dari gated latch yang memiliki dua input, yaitu DATA dan ENABLE. Ketika enable input disetel ke 1, inputnya sama dengan input Data. Jika tidak, tidak ada perubahan dalam output.

Kita dapat mendesain gated D latch dengan menggunakan gated SR latch. Input set dan reset dihubungkan bersama menggunakan inverter. Dengan melakukan ini, output akan berlawanan satu sama lain. Di bawah ini adalah diagram sirkuit dari Gated D Latch.

Circuit Diagram

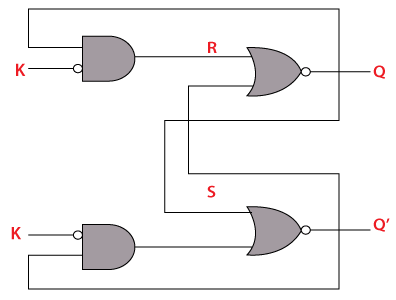

JK Latch

JK Latch sama dengan SR Latch. Di JK latch, status yang tidak jelas dihilangkan, dan output dialihkan ketika input JK high. Satu-satunya perbedaan antara SR latch JK latch adalah bahwa tidak ada umpan balik output terhadap input di SR latch, tetapi ada di JK latch. Diagram rangkaian dan tabel kebenaran kait JK adalah sebagai berikut:

Truth Table

Circuit Diagram

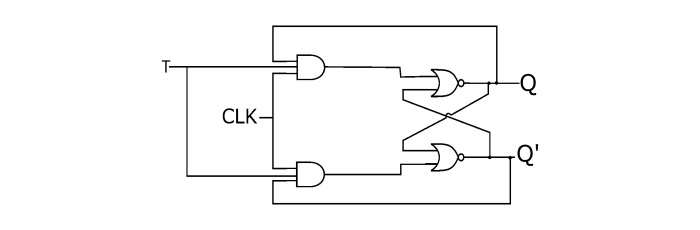

T Latch

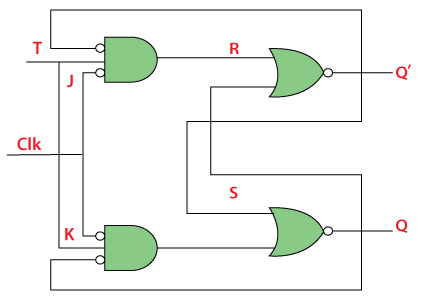

T latch terbentuk dengan menyingkat input JK latch. Keluaran dari T latch beralih ketika input disetel ke 1 atau high. Di bawah ini adalah diagram rangkaian T latch.

Circuit Diagram

Flip-Flops

A flip-flop is a sequential digital electronic circuit having two stable states that can be used to store one bit of binary data. Flip-flops are the fundamental building blocks of all memory devices.

Jenis-Jenis Flip-Flop

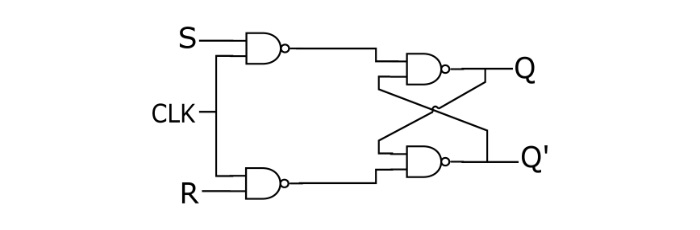

S-R Flip-flop

Ini adalah rangkaian flip-flop yang paling sederhana. Ini memiliki input set (S) dan input reset (R). Ketika di sirkuit ini ketika S diatur sebagai aktif, output Q akan tinggi dan Q' akan rendah. Jika R diatur ke aktif maka output Q rendah dan Q' tinggi. Setelah output ditetapkan, hasil rangkaian dipertahankan sampai S atau R berubah, atau daya dimatikan.

Truth table of S-R flip-flop

S R Q State

0 0 0 No Change

0 1 0 Reset

1 0 1 Set

1 1 X

Characteristics Table of S-R flip-flop

S R Q(t) Q(t+1)

0 0 0 0

0 0 1 1

0 1 0 0

0 1 1 0

1 0 0 1

1 0 1 1

1 1 0 X

1 1 1 X

Characteristics equation of S-R flip-flop

$$\mathrm{Q(t+1)=S+R`Q(t)}$$

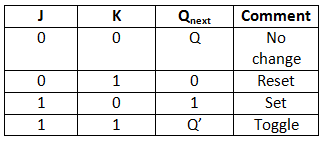

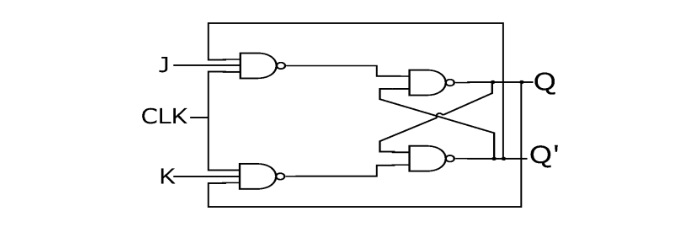

J-K Flip-flop

Karena keadaan tidak valid yang berhubungan dengan S=R=1 pada flip-flop SR, ada kebutuhan flip-flop lain. Flip-flop JK beroperasi hanya dengan transisi jam positif atau negatif. Operasi flip-flop JK mirip dengan flip-flop SR. Ketika input J dan K berbeda maka output Q mengambil nilai J pada clock edge berikutnya. Ketika J dan K keduanya rendah maka NO terjadi perubahan pada output. Jika J dan K keduanya tinggi, maka pada tepi jam, output akan beralih dari satu keadaan ke keadaan lainnya.

Truth table of JK flip-flop

J K Q State

0 0 0 No Change

0 1 0 Reset

1 0 1 Set

1 1 Toggles Toggle

Characteristics table of JK flip-flop

J K Q(t) Q(t+1)

0 0 0 0

0 0 1 1

0 1 0 0

0 1 1 0

1 0 0 1

1 0 1 1

1 1 0 1

1 1 1 0

Characteristics equation of JK flip-flop

$$\mathrm{Q(t+1)=jkQ(t)`+K`Q(t)}$$

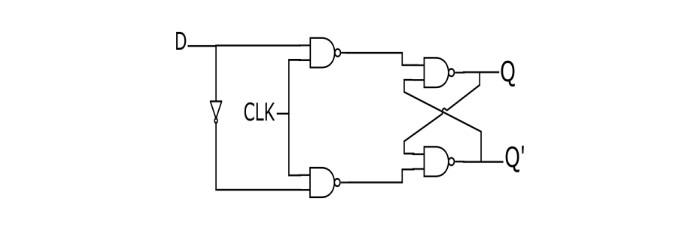

D Flip-flop

Dalam flip-flop D, output hanya dapat diubah pada transisi jam positif atau negatif, dan ketika input diubah pada waktu lain, output akan tetap tidak terpengaruh. D Flip-Flop umumnya digunakan untuk register geser dan pencacah. Perubahan keadaan keluaran D flip-flop tergantung pada transisi aktif jam. Output (Q) sama dengan input dan hanya berubah pada jam transisi aktif.

Truth table of D flip-flop

D Q

0 0

1 1

Characteristics equation of D flip-flop

$$\mathrm{Q(t+1)=D}$$

T Flip-flop

T Flip-flop (Toggle Flip-flop) adalah versi sederhana dari flip-flop JK. T flop diperoleh dengan menghubungkan input J dan K secara bersamaan. Flip-flop memiliki satu terminal input dan input clock. Flip-flop ini disebut T flip-flop karena kemampuannya untuk mengubah keadaan input. Toggle flip-flop kebanyakan digunakan di counter.

Truth Table of T flip-flop

T Q(t) Q(t+1)

0 0 0

0 1 1

1 0 1

1 1 0

Characteristics equation of T flip-flop

$$\mathrm{Q(t+1)=T'Q(t)+TQ(t)'=T\oplus Q(t)}$$

Applications of Flip-flops

- Counters

- Shift Registers

- Storage Registers, etc.

Timer

Contoh Soal & Jawaban:

1. Sebuah S-R latch input HIGH aktif dibentuk oleh cross-coupling dari

a) dua gerbang NOR

b) dua gerbang NAND

c) dua gerbang OR

d) dua gerbang AND

Jawaban: A.

2. Untuk kombinasi input D dan EN apa yang akan direset D latch?

a) D = LOW, EN = LOW

b) D = LOW, EN = HIGH

c) D = HIGH, EN = LOW

d) D = HIGH, EN = HIGH

Jawaban: B.

3. Sebuah flip-flop mengubah keadaannya selama

a) siklus operasional lengkap

b) tepi jatuh dari dorongan waktu

c) tepi naik dari dorongan waktu

d) 3 inputs and 3 outputs

Jawaban: D.

4. Tujuan dari input clock ke flip-flop adalah untuk

a) bersihkan perangkat

b) mengatur perangkat

c) selalu menyebabkan output berubah status

d) menyebabkan output mengasumsikan keadaan bergantung pada input pengontrol (J-K atau D).

Jawaban: D.

5. Untuk D flip-flop dipicu oleh tepi,

a) perubahan keadaan flip-flop hanya dapat terjadi pada tepi dorongan clock

b) keadaan flip-flop bergantung pada input D

c) output mengikuti input pada setiap dorongan clock

d) semua jawaban benar

Jawaban: D.

6. Ciri yang membedakan J-K flip-flop dari D flip-flop adalah.

a) toggle condition

b) preset input

c) type of clock

d) clear input

Jawaban: A.

7. Sebuah flip-flop SET ketika

a) J = 0, K = 0

b) J = 0, K = 1

c) J = 1, K = 0

d) J = 1, K = 1

Jawaban: C.

8. J-K flip-flop dengan J = 1 dan K = 1 memiliki input clock 10 kHz. Output Q adalah

a) terus-menerus HIGH

b) terus-menerus LOW

c) gelombang persegi 10 kHz

d) gelombang persegi 5 kHz

Jawaban: D.

9. J-K flip-flop dapat dibuat dari S-R flip-flop dengan menggunakan dua tambahan

a) AND gate

b) OR gate

c) NOT gate

d) NOR gate

Jawaban: A.

10. Latch yang dibangun dengan gerbang NOR dan NAND cenderung tetap dalam kondisi terkunci karena fitur konfigurasi yang mana?

a) Asynchronous operation

b) low input voltage

c) gate impedance

d) cross coupling

Jawaban: B.

Sumber:

> https://www.javatpoint.com/latches-in-digital-electronics

> https://www.tutorialspoint.com/digital_circuits/digital_circuits_flip_flops.htm

> https://electricalvoice.com/latches-flip-flops-and-timers-mcqs/

>

Comments

Post a Comment