Register

Register

Flip-flop adalah sel memori 1 bit yang dapat digunakan untuk menyimpan data digital. Untuk meningkatkan kapasitas penyimpanan dalam hal jumlah bit, kita harus menggunakan sekelompok flip-flop. Kelompok flip-flop seperti itu dikenal sebagai Register. Register n-bit akan terdiri dari n jumlah flip-flop dan mampu menyimpan kata n-bit.

Data biner dalam register dapat dipindahkan di dalam register dari satu flip-flop ke flip-flop lainnya. Register yang memungkinkan transfer data tersebut disebut sebagai register geser. Ada empat mode operasi register geser.

Masukan Serial Keluaran Seri

Masukan Serial Keluaran Paralel

Output Serial Input Paralel

Masukan Paralel Keluaran Paralel

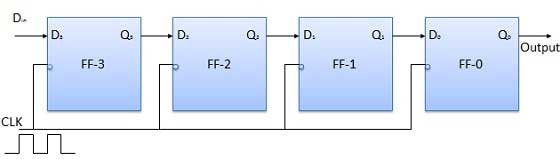

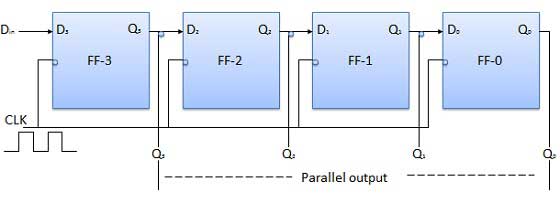

Masukan Serial Keluaran Seri

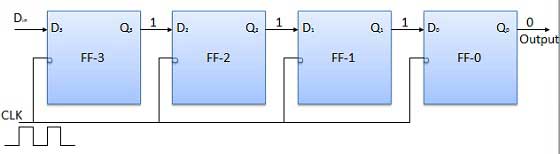

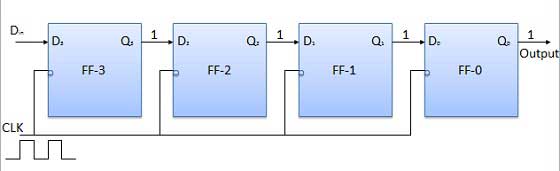

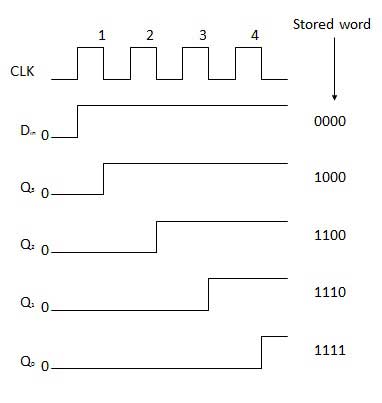

Biarkan semua flip-flop awalnya dalam kondisi reset yaitu Q3 = Q2 = Q1 = Q0 = 0. Jika entri bilangan biner empat bit 1 1 1 1 dibuat ke dalam register, nomor ini harus diterapkan ke bit Din dengan bit LSB diterapkan terlebih dahulu. Input D dari FF-3 yaitu D3 terhubung ke input data serial Din. Output dari FF-3 yaitu Q3 terhubung ke input flip-flop berikutnya yaitu D2 dan seterusnya.

Diagram Blok

Operasi

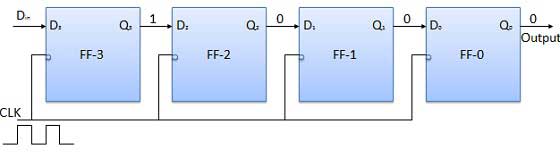

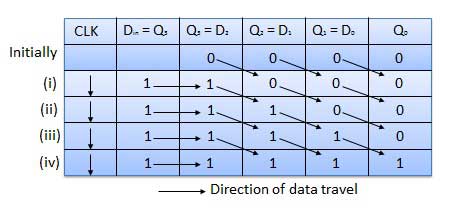

Sebelum penerapan sinyal clock, biarkan Q3 Q2 Q1 Q0 = 0000 dan terapkan bit LSB dari nomor yang akan dimasukkan ke Din. Jadi Din = D3 = 1. Terapkan jam. Pada tepi jatuh pertama jam, FF-3 diatur, dan kata yang disimpan dalam register adalah Q3 Q2 Q1 Q0 = 1000.

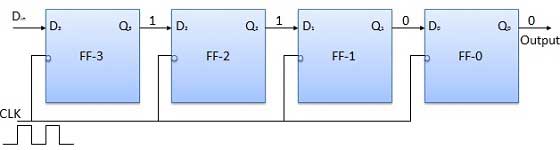

Terapkan bit berikutnya ke Din. Jadi Din = 1. Segera setelah tepi negatif jam berikutnya menyentuh, FF-2 akan disetel dan kata yang disimpan berubah menjadi Q3 Q2 Q1 Q0 = 1100.

Terapkan bit berikutnya yang akan disimpan yaitu 1 ke Din. Terapkan pulsa jam. Segera setelah tepi jam negatif ketiga menyentuh, FF-1 akan disetel dan keluaran akan dimodifikasi menjadi Q3 Q2 Q1 Q0 = 1110.

Demikian pula dengan Din = 1 dan dengan kedatangan tepi jam negatif keempat, kata yang disimpan dalam register adalah Q3 Q2 Q1 Q0 = 1111.

Truth Table

Waveforms

Masukan Serial Keluaran Paralel

Dalam jenis operasi seperti itu, data dimasukkan secara serial dan dikeluarkan secara paralel.

Data dimuat sedikit demi sedikit. Output dinonaktifkan selama data sedang dimuat.

Segera setelah pemuatan data selesai, semua flip-flop berisi data yang diperlukan, output diaktifkan sehingga semua data yang dimuat tersedia di semua jalur output pada saat yang bersamaan.

4 siklus clock diperlukan untuk memuat kata empat bit. Oleh karena itu kecepatan operasi mode SIPO sama dengan mode SISO.

Block Diagram

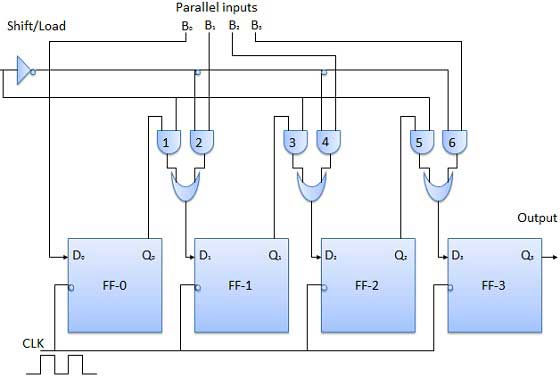

Output Serial Input Paralel (PISO)

Bit data dimasukkan secara paralel.

Rangkaian yang ditunjukkan di bawah ini adalah register output serial input paralel empat bit.

Output dari Flip Flop sebelumnya terhubung ke input berikutnya melalui rangkaian kombinasional.

Kata masukan biner B0, B1, B2, B3 diterapkan melalui rangkaian kombinasional yang sama.

Ada dua mode di mana rangkaian ini dapat bekerja yaitu - mode shift atau mode beban.

Mode muat

Ketika garis shift/load bar rendah (0), gerbang AND 2, 4 dan 6 menjadi aktif mereka akan melewatkan bit B1, B2, B3 ke flip-flop yang sesuai. Pada tepi jam yang rendah, input biner B0, B1, B2, B3 akan dimuat ke dalam flip-flop yang sesuai. Dengan demikian terjadi pembebanan paralel.

Pergeseran mode

Ketika garis shift/load bar rendah (1), gerbang AND 2, 4 dan 6 menjadi tidak aktif. Oleh karena itu pemuatan paralel data menjadi tidak mungkin. Tetapi gerbang AND 1,3 dan 5 menjadi aktif. Oleh karena itu pergeseran data dari kiri ke kanan sedikit demi sedikit pada aplikasi pulsa clock. Dengan demikian, operasi paralel dalam serial keluar terjadi.

Diagram Blok

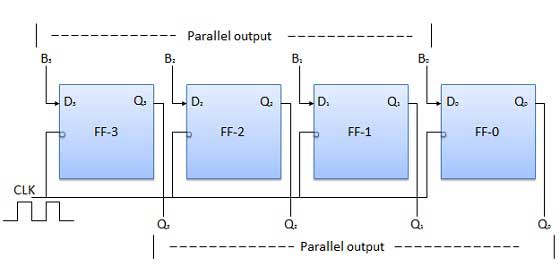

Masukan Paralel Keluaran Paralel (PIPO)

Dalam mode ini, input biner 4 bit B0, B1, B2, B3 diterapkan ke input data D0, D1, D2, D3 masing-masing dari empat flip-flop. Segera setelah tepi jam negatif diterapkan, bit biner input akan dimuat ke dalam flip-flop secara bersamaan. Bit yang dimuat akan muncul secara bersamaan ke sisi output. Hanya pulsa clock yang penting untuk memuat semua bit.

Diagram Blok

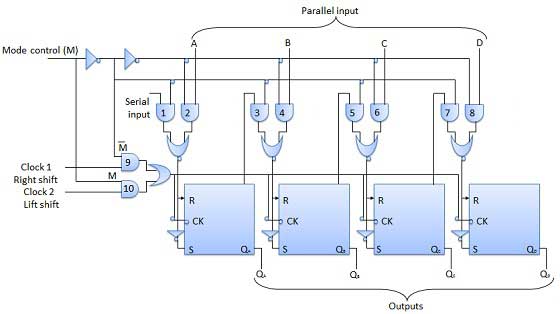

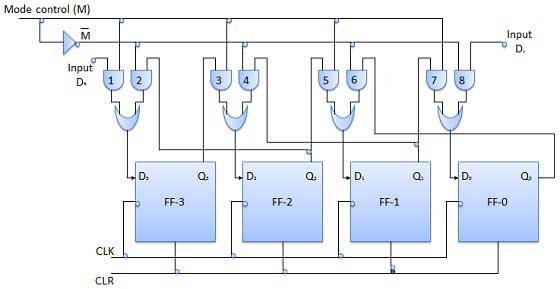

Daftar Shift Dua Arah

Jika suatu bilangan biner digeser ke kiri satu posisi maka sama dengan mengalikan bilangan asli dengan 2. Begitu pula jika bilangan biner digeser ke kanan satu posisi maka sama dengan membagi bilangan asli dengan 2.

Oleh karena itu jika kita ingin menggunakan register geser untuk mengalikan dan membagi bilangan biner yang diberikan, maka kita harus dapat memindahkan data ke arah kiri atau kanan.

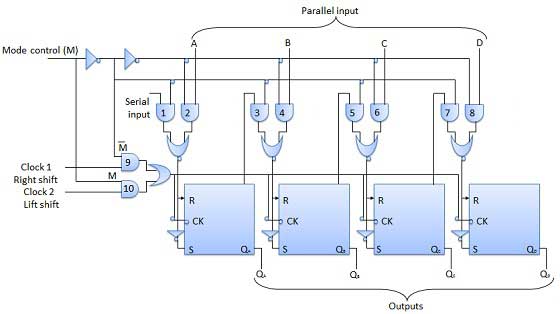

Register semacam itu disebut register dua arah. Sebuah register geser empat bit dua arah ditunjukkan pada gambar.

Terdapat dua input serial yaitu input data geser kanan serial DR, dan input data geser kiri serial DL beserta input pemilihan mode (M).

Diagram Blok

Operation

| S.N. | Condition | Operation |

|---|

| 1 | With M = 1 − Shift right operation | Jika M = 1, maka gerbang AND 1, 3, 5 dan 7 diaktifkan sedangkan gerbang AND 2, 4, 6 dan 8 yang tersisa akan dinonaktifkan.

Data pada DR digeser ke kanan sedikit demi sedikit dari FF-3 ke FF-0 pada aplikasi pulsa clock. Jadi dengan M = 1 kita mendapatkan operasi shift kanan serial. |

| 2 | With M = 0 − Shift left operation | Ketika kontrol mode M terhubung ke 0 maka gerbang AND 2, 4, 6 dan 8 diaktifkan sementara 1, 3, 5 dan 7 dinonaktifkan.

Data pada DL digeser ke kiri sedikit demi sedikit dari FF-0 ke FF-3 pada aplikasi pulsa clock. Jadi dengan M = 0 kita mendapatkan operasi shift kanan serial. |

Register Geser Universal

Register geser yang dapat menggeser data hanya dalam satu arah disebut register geser uni-directional. Register geser yang dapat menggeser data ke dua arah disebut register geser dua arah. Menerapkan logika yang sama, register geser yang dapat menggeser data di kedua arah serta memuatnya secara paralel, dikenal sebagai register geser universal. Register geser mampu melakukan operasi berikut:

Pemuatan paralel

Pergeseran Kiri

Pergeseran kanan

Input kontrol mode terhubung ke logika 1 untuk operasi pembebanan paralel sedangkan terhubung ke 0 untuk pemindahan serial. Dengan pin kontrol mode terhubung ke ground, register geser universal bertindak sebagai register dua arah. Untuk operasi kiri serial, input diterapkan ke input serial yang menuju ke gerbang AND-1 yang ditunjukkan pada gambar. Sedangkan untuk operasi shift kanan, input serial diterapkan pada input D.

Diagram Blok

Contoh Soal & Jawaban:

1. Sebuah S-R latch input HIGH aktif dibentuk oleh cross-coupling dari

a) dua gerbang NOR

b) dua gerbang NAND

c) dua gerbang OR

d) dua gerbang AND

Jawaban: A.

2. Untuk kombinasi input D dan EN apa yang akan direset D latch?

a) D = LOW, EN = LOW

b) D = LOW, EN = HIGH

c) D = HIGH, EN = LOW

d) D = HIGH, EN = HIGH

Jawaban: B.

3. Sebuah flip-flop mengubah keadaannya selama

a) siklus operasional lengkap

b) tepi jatuh dari dorongan waktu

c) tepi naik dari dorongan waktu

d) 3 inputs and 3 outputs

Jawaban: D.

4. Tujuan dari input clock ke flip-flop adalah untuk

a) bersihkan perangkat

b) mengatur perangkat

c) selalu menyebabkan output berubah status

d) menyebabkan output mengasumsikan keadaan bergantung pada input pengontrol (J-K atau D).

Jawaban: D.

5. Untuk D flip-flop dipicu oleh tepi,

a) perubahan keadaan flip-flop hanya dapat terjadi pada tepi dorongan clock

b) keadaan flip-flop bergantung pada input D

c) output mengikuti input pada setiap dorongan clock

d) semua jawaban benar

6. Ciri yang membedakan J-K flip-flop dari D flip-flop adalah.

a) toggle condition

b) preset input

c) type of clock

d) clear input

7. Sebuah flip-flop SET ketika

a) J = 0, K = 0

b) J = 0, K = 1

c) J = 1, K = 0

d) J = 1, K = 1

8. J-K flip-flop dengan J = 1 dan K = 1 memiliki input clock 10 kHz. Output Q adalah

a) terus-menerus HIGH

b) terus-menerus LOW

c) gelombang persegi 10 kHz

d) gelombang persegi 5 kHz

9. J-K flip-flop dapat dibuat dari S-R flip-flop dengan menggunakan dua tambahan

a) AND gate

b) OR gate

c) NOT gate

d) NOR gate

10. Latch yang dibangun dengan gerbang NOR dan NAND cenderung tetap dalam kondisi terkunci karena fitur konfigurasi yang mana?

a) Asynchronous operation

b) low input voltage

c) gate impedance

d) cross coupling

Jawaban: B.

Sumber:

> https://onlinelearning.uhamka.ac.id

> https://www.tutorialspoint.com/computer_logical_organization/digital_registers.htm#

> https://testbook.com/objective-questions/mcq-on-register--5eea6a1439140f30f369f2ae

Comments

Post a Comment